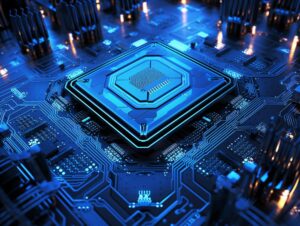

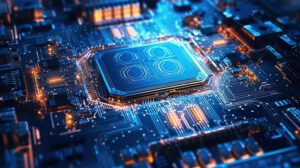

In semiconductor design, the intricate process of creating Application-Specific Integrated Circuits (ASICs) involves a systematic sequence of steps known as the ASIC flow in VLSI (Very Large Scale Integration). This meticulously structured procedure encompasses various stages, each playing a pivotal role in shaping the final ASIC product. Understanding the ASIC flow in VLSI is paramount for engineers and designers aiming to craft custom integrated circuits tailored to specific applications.

In today’s article, we will examine the ASIC flow sequentially and understand its importance in creating specialized integrated circuits catering to versatile applications in today’s technological landscape.

ASIC Design Flow Sequence

Collecting Product Requirements And Specifications

The first step in the ASIC design flow involves collecting the requirements and specifications regarding the desired product from the client and determining the resources required to complete the project successfully while also capturing the software and hardware features to be implemented.

Architecture

A system-level view of how the chip should operate is provided by the architects at this stage. They also take a call regarding any additional component requirements, targeting energy and power requirements, and more importantly the data flow inside the chip. To give an example it could involve the way the data flows when the processor fetches imaging data from the system RAM and executes them.

Digital Design

It is not feasible to manufacture from scratch owing to the complex nature of microchips, to solve this issue a behavioral description is developed to analyze the design in terms of functionality, performance, and other high-level issues using a hardware description language such as Verilog and VHDL. This is usually done by a digital designer possessing skillsets at par with a software engineer.

Functional Verification

This involves testing the ASIC to ensure it meets the intended requirements and specifications. The RTL code is verified in terms of its functionality using testbench in a technique called behavioral simulation. A good testbench usually achieves more than 90% code coverage.

RTL block synthesis

The RTL code generated in the previous stages is converted into a gate-level netlist. This is referred to as synthesis which is carried forward through the use of a synthesis tool that converts the RTL code into a gate-level representation of the design. The gate-level netlist is reviewed and optimized to ensure it meets the desired requirements.

For those looking for assistance to land RTL Design jobs reach out to us through our official website.

Chip Partitioning

This is the phase where the chip is divided or partitioned into small blocks to make it easier to place and route on the functional block. This can be implemented at the logical design phase where the design is divided into sub-blocks for development or at the physical design phase to aid in placement and routing activities.

Design for Test (DFT) Insertion

ASIC design is filled with complexities at every stage of the cycle making it imperative to subject the design to techniques such as scan path insertion, memory built-in -self-test, and automatic test pattern generation to keep pace with increasing system-on-chip variations such as size, threshold voltage, and wire resistance.

To fine-tune your DFT skills enroll in our DFT course at the earliest to get attractive discounts!

Floor Planning

It refers to the process of arranging blocks on a chip. It consists of the following steps: block placement, design portioning, pin placement, and power optimization.

The floor plan specifies the size of the chip, where the gates are placed, and how they are wired together. Engineers consider wire length and functioning while connecting to ensure that signals do not interfere with surrounding elements. Finally, use the post-layout verification process to replicate the final floor plan.

Placement

Placement is the process of placing standard cells in a row. A poor placement requires a larger area and also degrades performance. Various factors, like the timing requirement, the net lengths, and hence the connections of cells, power dissipation should be taken care of. It removes timing violations.

Clock tree synthesis

A clock tree is a clock distribution network within a system or hardware design, it includes the clock circuitry and devices from clock source to destination. Clock tree synthesis is the technique used to insert automatic buffers along the clock path of the ASIC design to synchronize the clock delay across all the components or modules in a chip. It is used to aid in achieving accurate timing and optimizing power consumption within a complex integrated circuit.

Routing

Routing is the process of creating physical connections between or among the signal pins by following DRC rules and also routing timing (setup and hold) have to meet.

Physical and Timing Verification

Following routing, the ASIC design layout goes through three physical verification procedures known as signoff checks. This stage assists in determining whether the layout is functioning as intended. To avoid errors right before the tape out, the following checks are performed namely Layout versus schematic, design rule checks, and layout versus schematic. Timing verification is done to make sure that the chip runs at the desired frequency.

The ASIC flow in VLSI encapsulates a thorough and systematic sequence of stages essential for producing specialized integrated circuits. Each phase, from initial planning and design to production, is critical in molding the final ASIC product. Understanding and properly executing the ASIC cycle is critical for engineers seeking to design specialized integrated circuits tailored to a wide range of applications in today’s technological world.

Are you a VLSI aspirant struggling to find time to prepare for entrance exams, Enroll in our VLSI training online to learn at your convenience.