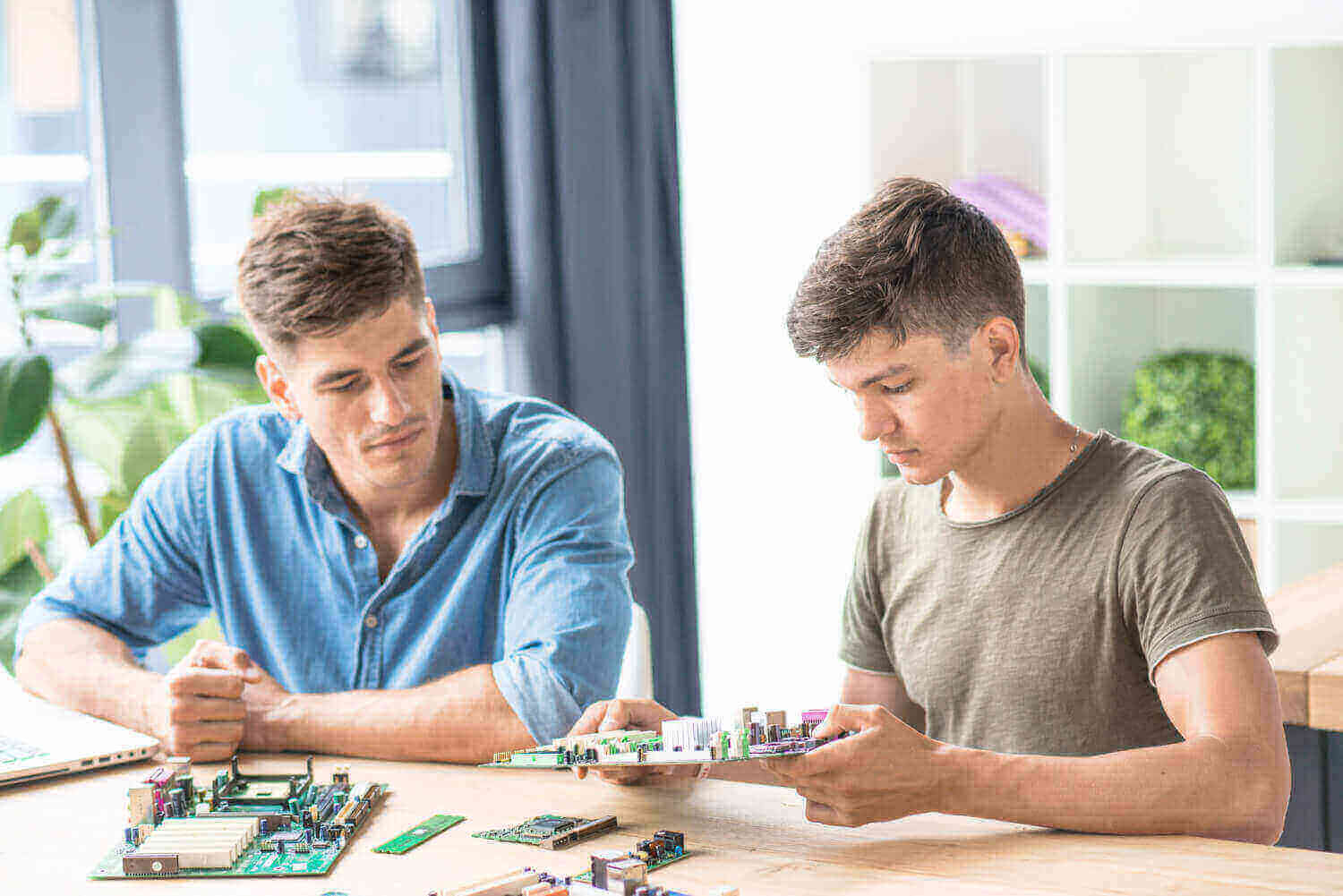

Latch-up is a critical reliability concern in Very Large Scale Integration (VLSI) systems, which can lead to device failure and increased power consumption. Understanding how to diagnose and prevent latch-up is essential for ensuring the longevity and performance of integrated circuits (ICs).

For those interested in mastering these concepts, enrolling in a VLSI course can provide a solid foundation.

In this blog, you’ll find the steps to diagnose latch-up issues in VLSI systems effectively. Before going through the diagnostic steps, it’s very important to understand what latch-up is. Latch-up is a condition where a parasitic thyristor, formed within the CMOS structure, is unintentionally triggered, leading to a low-impedance path between the power supply and the ground. This can cause excessive current flow, potentially damaging the IC if not addressed promptly.

Steps to Diagnose Latch-Up in VLSI

1. Identifying the Symptoms of Latch-Up

The first step in diagnosing latch-up is recognizing its symptoms. These can include:

- A sudden increase in power consumption.

- Abnormal voltage levels across the IC.

- Overheating of the chip.

- Permanent damage to the IC after a latch-up event.

Observing these symptoms during testing or operation is a strong indicator that latch-up might be occurring.

2. Analyzing the IC Layout and Design

Next, review the IC layout and design. Latch-up is more likely to occur in certain configurations, such as:

- Inadequate spacing between N-well and P-well regions.

- Poorly designed guard rings.

- High substrate resistivity.

A detailed examination of the design can help identify potential latch-up hotspots. Understanding these aspects is often covered in a complete VLSI design course.

3. Performing Electrical Testing

Conduct electrical tests under various conditions to provoke a latch-up event. Key tests include:

- Power Supply Ramp-Up/Down Tests: Slowly tilt up and down the power supply voltage to see if latch-up is triggered.

- ESD Testing: Electrostatic Discharge (ESD) events can induce latch-up. Simulating ESD conditions during testing can help identify vulnerabilities.

- Temperature Variation Tests: Increasing the temperature of the IC can lower the threshold for latch-up, making it easier to diagnose.

4. Implementing Physical Analysis Techniques

If electrical testing indicates latch-up, physical analysis can help pinpoint the exact location and cause. Techniques include:

- Infrared (IR) Thermography: This can identify hot spots in the IC where latch-up may be occurring.

- Emission Microscopy: Useful for detecting light emissions from the latch-up event.

- Cross-Sectional Analysis: Provides a detailed view of the IC’s structure, which can reveal layout issues contributing to latch-up.

5. Reviewing Power Supply Decoupling

Improper power supply decoupling can worsen latch-up conditions. Review the decoupling strategy used in the IC design:

- Ensure adequate decoupling capacitors are in place.

- Verify that the capacitors are correctly positioned to minimize the inductance between the power supply and ground.

6. Employing Simulation Tools

Simulation tools can predict latch-up vulnerability before physical testing. Use tools like SPICE to simulate the behavior of the IC under various conditions. This can help identify potential latch-up issues early in the design phase, saving time and resources.

7. Implementing Design and Process Solutions

Once the latch-up issues are diagnosed, implementing design or process changes is necessary to prevent recurrence. Solutions include:

- Guard Rings: Adding or improving guard rings around sensitive areas can help contain latch-up.

- Substrate Contacts: Increase the number of substrate contacts to reduce the resistance and suppress latch-up.

- Well Taps: Proper placement of well taps can prevent latch-up by ensuring that the N-well and P-well regions are well-controlled.

Conclusion

Diagnosing latch-up in VLSI systems requires a combination of understanding the phenomenon, careful design analysis, thorough electrical testing, and the use of advanced diagnostic tools. By following these steps, engineers can effectively identify and mitigate latch-up issues, ensuring the reliability and performance of their VLSI designs. For those looking to deepen their understanding, enrolling in a VLSI online course can be an excellent way to build the necessary skills and knowledge.