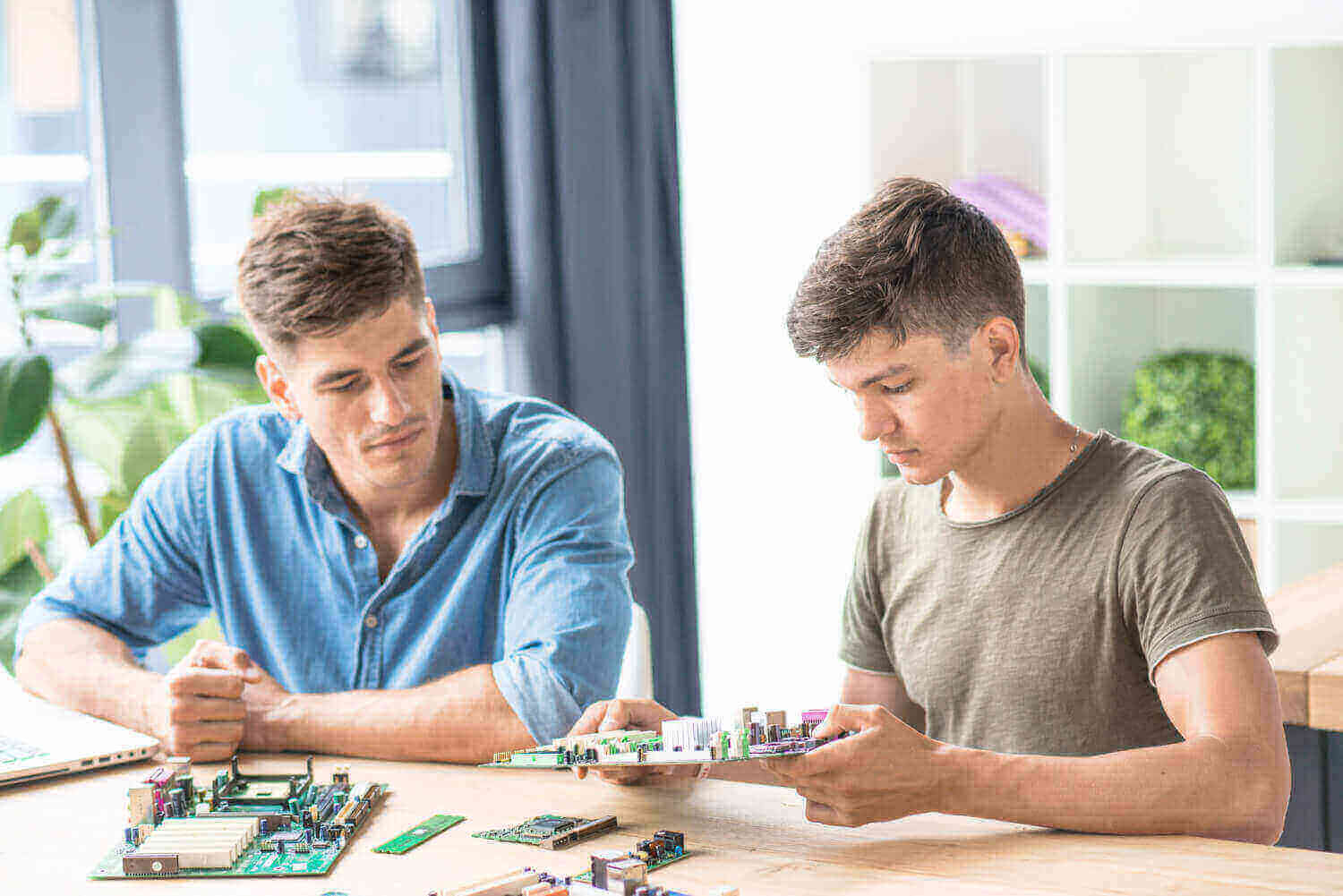

Because hardware designs are becoming increasingly complicated, the old technique of manually writing tests to validate the designs, i.e. the Directed Test approach, is becoming increasingly difficult to implement and maintain for larger and more sophisticated systems. There are some corner scenarios that are either impossible to anticipate, code test for, or are overlooked during verification. Visual analysis of waveforms to track out a design flaw is always a time-consuming operation. Today, the time we spend on verification has surpassed the time we spent on design, accounting for about 70% of the entire development effort.

What is SystemVerilog?

SystemVerilog is a Verilog extension with several verification tools that allow engineers to test their designs in simulation utilizing complicated testbench architectures and random stimuli. SystemVerilog is a hardware description and verification language that is used to describe, develop, simulate, test, and implement electronic systems. It is standardized as IEEE 1800.

What is Verification? Why is Verification Done?

In this blog, we have come up with a detailed overview of the SV Verification guide in VLSI.

Engineers test the design to ensure that it is an accurate representation of the requirements and free of errors. Verification is done to guarantee that the design is proper, to avoid surprises later on, to avoid a re-spin of the chip, and to ensure that the chip is released on schedule and in excellent condition.

Engineers test the design’s behavior by driving both a correct and an incorrect input. In both circumstances, they monitor the design to see whether it is performing as predicted; if it isn’t, then there is a defect.

Software for verification and synthesis:

SystemVerilog is frequently used in the semiconductor design industry for design verification. SystemVerilog has been integrated into the mixed-language HDL simulators of the three main EDA suppliers (Cadence Design Systems, Mentor Graphics, and Synopsys). Although no simulator can claim to handle the whole SystemVerilog, making testbench interoperability difficult, efforts are underway to encourage cross-vendor compatibility. Open Verification Methodology is an open-source class library that uses a framework that makes it easier to create reusable testbenches and pre-made verification-IP. The Testbench/Verification environment is used in verification to assess the accuracy of the design under test (DUT).

What is The Use of SystemVerilog Verification?

SystemVerilog adoption has been modest in the design synthesis role (translation of a hardware design description into a gate-netlist). Many design teams employ design processes that entail the usage of many tools from various suppliers. Most design teams won’t be able to switch to SystemVerilog RTL design until all of their front-end tools (linters, formal verification, and automated test structure generators) support the same language subset.

Conclusion:

UVM and SystemVerilog have grown in popularity and adoption by a significant number of semiconductor companies in recent years to address productivity, performance, and bug-free designs. Another positive aspect is that UVM and SystemVerilog have been widely adopted by the EDA and verification communities.

Chipedge, a VLSI training institute brings for you the Online VLSI SV Verification Guide Course that begins with a thorough review of functional verification approaches and the SystemVerilog language, before delving into the specifics of creating a class-based verification environment with SystemVerilog HDVL. It includes thorough training on designing testbenches using OOP, constraint random simulation, and verification sign-off using functional coverage as part of the SystemVerilog for Verification module. Finally, it introduces UVM methodology ideas and discusses why IEEE standard techniques like UVM are necessary for creating SystemVerilog-based testbenches.

Learn more in detail by registering for online VLSI courses on Chipedge which is the best VLSI training institute in India for online VLSI training. There are several online VLSI courses on this website for starting a successful career in VLSI industry. This VLSI training institute offers various VLSI job oriented courses like Physical Design course, Design Verification course, ASIC verification course, DFT course , chip design course and many more. Register yourself for the best courses today!

Image Source